Goepel electronic presents new pre-configured JTAG test and programming solutions.

These complete solutions are especially useful for fast verification of electronic prototypes in the laboratory or high mix/low volume assembly test.

The SCANBOOSTER II Studio Bundles are based on a powerful embedded JTAG controller combined with a special edition of the integrated development environment SYSTEM CASCON.

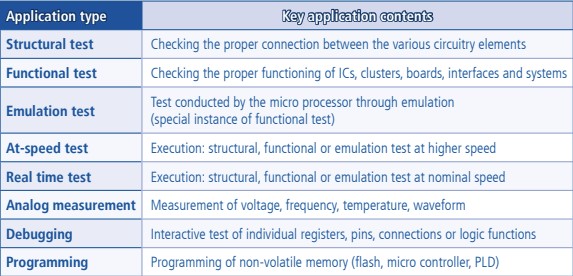

The SCANBOOSTER II controller works with modern multi-core processors and FPGA to supports a wide range of embedded technologies. These test and validation methods use functions within integrated circuits to test and program complex PCB assemblies with little physical access.

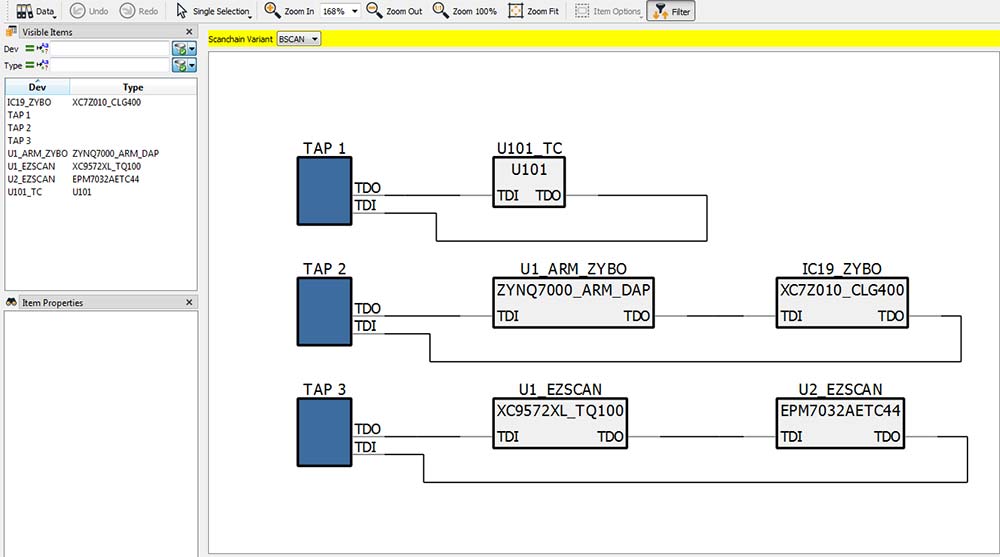

In the bundle, the controller offers two independent, truly parallel Test Access Ports (TAP) with TCK up to 16MHz. To supplement the JTAG access, the controller also contains 32 channels of programmable multifunctional I/O for testing via connectors and testpoints.

This enables the synchronized execution of embedded test, debug and programming operations via Boundary Scan (IEEE1149.x), processor emulation, Chip Integrated Instruments or the Embedded Diagnostics procedure. Due to its small size, the controllers can be used as desktop devices as well as for integration into other system environments. USB2.0 and GBit LAN are available as standard control interfaces.

The software platform SYSTEM CASCON is available in three editions.

CASCON RunTime is offered as a pure test station. This allows all types of existing test programs to be executed.

For development stations you can choose between CASCON GALAXY DS BASE/SX and CASCON GALAXY DS STANDARD/SX.

The DS BASE Edition provides Boundary Scan entry-level tools for automatic test program generation (ATPG) and pin failure diagnostics (PFD) for infrastructure and interconnection test it also comes with numerous boundary scan debug tools.

The DS-STANDARD Edition enhances this capability by including ATPG & PFD for memory devices and device model tests. Also included are the ISP (In-System Programming) routines and the powerful Test Coverage Analyzer.

If you want to find out more about the JTAG/Boundary Scan technology, please download our white paper.

Contact us for more information or a demonstration on your electronic board!